Giải Công nghệ 12 Cánh diều Bài 22. Mạch xử lí tín hiệu trong điện tử số có đáp án

51 người thi tuần này 4.6 459 lượt thi 7 câu hỏi

Bạn cần đăng ký gói VIP ( giá chỉ từ 250K ) để làm bài, xem đáp án và lời giải chi tiết không giới hạn.

🔥 Học sinh cũng đã học

Đề thi Cuối kì 2 Công nghệ 12 Lâm nghiệp thủy sản Kết nối tri thức cấu trúc mới có đáp án - Đề 3

Đề thi Cuối kì 2 Công nghệ 12 Lâm nghiệp thủy sản Kết nối tri thức cấu trúc mới có đáp án - Đề 2

Đề thi Cuối kì 2 Công nghệ 12 Lâm nghiệp thủy sản Kết nối tri thức cấu trúc mới có đáp án - Đề 1

Đề thi Cuối kì 2 Công nghệ 12 Điện - điện tử Kết nối tri thức cấu trúc mới có đáp án - Đề 3

Đề thi Cuối kì 2 Công nghệ 12 Điện - điện tử Kết nối tri thức cấu trúc mới có đáp án - Đề 2

Đề thi Cuối kì 2 Công nghệ 12 Điện - điện tử Kết nối tri thức cấu trúc mới có đáp án - Đề 1

Đề thi Giữa kì 2 Công nghệ 12 Lâm nghiệp thủy sản Kết nối tri thức cấu trúc mới có đáp án - Đề 3

Đề thi Giữa kì 2 Công nghệ 12 Lâm nghiệp thủy sản Kết nối tri thức cấu trúc mới có đáp án - Đề 2

Danh sách câu hỏi:

Lời giải

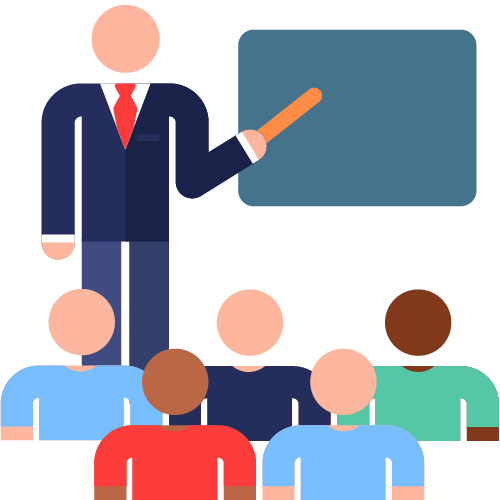

- Mạch xử lí tín hiệu số ở Hình 22.1 sử dụng các cổng logic sau:

+ Cổng AND

+ Cổng NOT

+ Cổng OR

+ Cổng AND

- Tín hiệu đầu ra Q ở dạng bit 0 và 1.

Lời giải

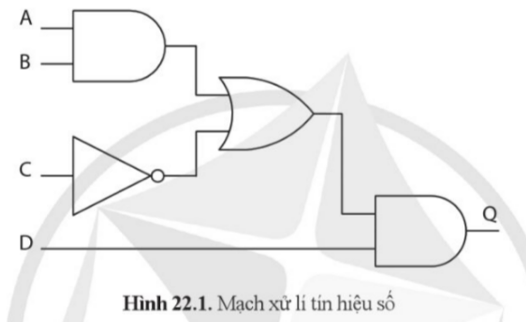

Chức năng của mạch so sánh tín hiệu số là:

Mạch so sánh xử lí tín hiệu số có đầu ra phụ thuộc vào tổ hợp các trạng thái của đầu vào.

Lời giải

Nếu A = 0 và B = 0 thì đầu ra của cổng logic C có kết quả là 0.

Lời giải

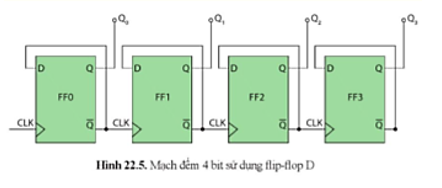

Nguyên lí hoạt động của mạch đếm tín hiệu số 4 bit sử dụng phần tử nhớ flip-flop:

Flip-flop D là phân tử điện tử hoạt động với hai trạng thái đặt và xoá, thường được biểu diễn tương ứng là giá trị 1 và 0. Flip-flop D có hai đầu vào, bao gồm đâu vào dữ liệu D và đâu vào xung nhịp CLK, hai đâu ra Q và Q .Hoạt động của flip-flop D được mô tả trên bảng chân lí (Bảng 22.2) và giản đồ thời gian .Trong đó, đâu ra Q phụ thuộc vào dữ liệu ở đầu vào D và xung nhịp CLK, cụ thể Q thay đổi trạng thái theo D khi CLK chuyển từ 0 sang 1.

Lời giải

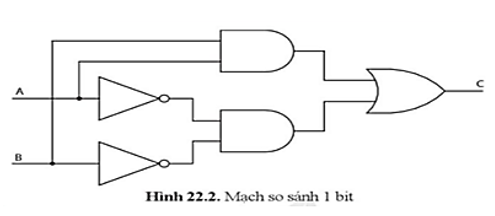

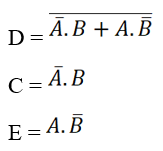

* Bảng chân lí của mạch so sánh Hình 22.7:

|

A |

B |

C |

D |

E |

|

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

0 |

* Phương trình logic của các tín hiệu đầu ra C, D, E:

Lời giải

Xác định giá trị đầu ra Q và số đếm thập phân:

- Chu kỳ xung nhịp thứ 5:

+ CLK = 1

+ Q0 = 1 (do CLK lên cao lần đầu tiên)

+ Q1 = 0 (giữ nguyên giá trị ban đầu)

+ Q2 = 0 (giữ nguyên giá trị ban đầu)

+ Q3 = 0 (giữ nguyên giá trị ban đầu)

Giá trị số đếm thập phân: 0000 (0)

- Chu kỳ xung nhịp thứ 6:

+ CLK = 1

+ Q0 = 1 (giữ nguyên giá trị)

+ Q1 = 1 (thay đổi trạng thái do Q0 chuyển từ 0 sang 1)

+ Q2 = 0 (giữ nguyên giá trị)

+ Q3 = 0 (giữ nguyên giá trị)

Giá trị số đếm thập phân: 0001 (1)

- Chu kỳ xung nhịp thứ 7:

+ CLK = 1

+ Q0 = 1 (giữ nguyên giá trị)

+ Q1 = 1 (giữ nguyên giá trị)

+ Q2 = 1 (thay đổi trạng thái do Q1 chuyển từ 0 sang 1)

+ Q3 = 0 (giữ nguyên giá trị)

Giá trị số đếm thập phân: 0010 (2)

Vậy ta có:

|

Giá trị đầu ra Q của từng flip-flop: |

Giá trị số đếm thập phân tương ứng: |

|

- Chu kỳ 5: Q0 = 1, Q1 = 0, Q2 = 0, Q3 = 0 - Chu kỳ 6: Q0 = 1, Q1 = 1, Q2 = 0, Q3 = 0 - Chu kỳ 7: Q0 = 1, Q1 = 1, Q2 = 1, Q3 = 0 |

- Chu kỳ 5: 0000 (0) - Chu kỳ 6: 0001 (1) - Chu kỳ 7: 0010 (2) |

Lời giải

Bạn cần đăng ký gói VIP ( giá chỉ từ 250K ) để làm bài, xem đáp án và lời giải chi tiết không giới hạn.

Xem tiếp với tài khoản VIP

Còn 1/7 câu hỏi, đáp án và lời giải chi tiết.

Bạn cần đăng ký gói VIP ( giá chỉ từ 250K ) để làm bài, xem đáp án và lời giải chi tiết không giới hạn.